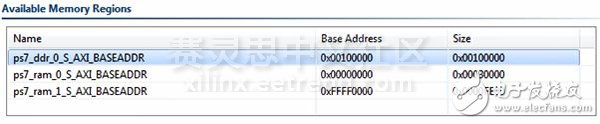

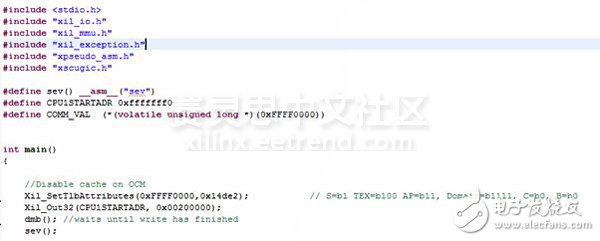

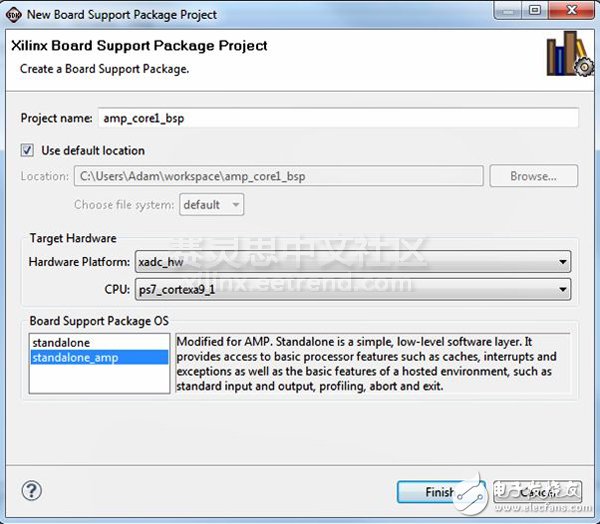

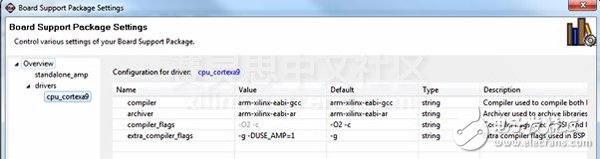

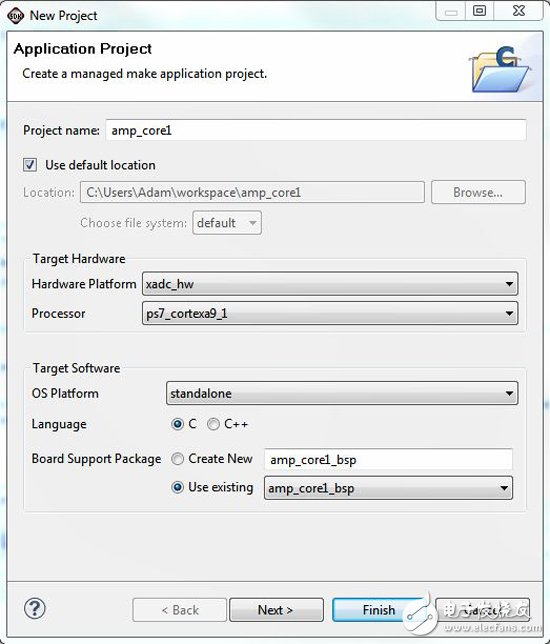

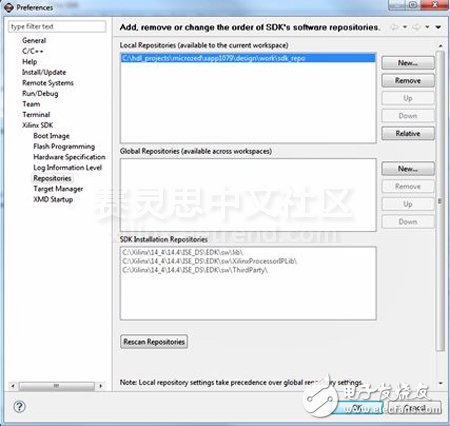

In my last blog, I introduced the concept of implementing an asymmetric multi-process processing model by using two ARM Cortex-A9 MPCore processors on the Zynq SoC to execute different task programs. I expect you to be able to sit because this blog is a bit long, but we will gain something, and in the end we will get our AMP system up and running, and we will do a lot of preparations before we can get the AMP system up and running. But these are very simple so don't worry. The key to building an AMP system on the Zynq SoC is to configure a boot loader. After the first stage loader is executed, the processor will look for the executable and load it into memory. Unfortunately, the Vivado tool I used is version 2014.1 (because I recently moved without a network so I can't download the latest version), this version does not support AMP when we generate FSBL (first stage boot load file), so in order to be able to complete For this example I will use the modified FSBL file and standalone OS file provided in Xilinx Application Note XAPP1079. (source file download link) After downloading the zip file, the first part is to extract the file to your desired working directory and rename the folder to SRC. These files contain the modified FSBL and standalone OS files. We need to let the SDK software find these files, so the next step is to set up an update to the SDK repository directory so that the SDK can find these files. In the SDK software menu, click on Xilinx tools, select repositories from the drop-down menu, and create a new repository file directory with the path <your working directory>\app1079\design\work\sdk_repo, as shown below: The next step after adding a good repository is to generate the following files: We want to generate a BSP (Board Support Package) file for each processor core: Next we have to create an application for the first processor core, which is equally simple. We have done this many times before, here to make sure to choose Core 0 and standalone OS and create your own BSP file. Once we have created the application for the kernel, we need to correctly define the mapped address of the DDR memory, since the program will execute from these addresses. We need to edit the link script as shown below to display the base address and size of the DDR memory. This step is very important. If we can't correctly define the memory address and size for Core 0 and Core 1, there will be conflicts between the kernels during the execution of the program, and a segment address error will occur. Now we can write the code for the Core 0 executor. This part is the core of the AMP system, which will execute the program code from Core 1. We need to include the following part of the code in our application code. This part of the code disables the cache function stored on the Zynq SoC on-chip. It defines the starting address of Core 1, which is within the memory mapped address range of Core 1. You can view the previously defined link script. Once Core 0 executes the Set Event (SEV) command, Core 1 will start executing the program code it is responsible for. The next step is to create a BSP file for Core 1, we will use the modified standalone OS template (standalone_amp), which disables the repeated initialization of the PS Control Unit (SCU). Therefore, we can't allow automatic generation of BSP files, which is different from Core 0's operation. Also, make sure that Core 1 is selected in the CPU's selection. Now that we have created the BSP file for Core 1, we have to modify some of the BSP settings before we write the application code for Core 1. This step is very simple and requires an additional compilation flag in the driver configuration dialog. ---–DUSE_AMP=1, the specific operation refers to the following figure: After doing this, we can create an application for Core 1. As shown in the figure below, make sure that the processor selects Core 1, and the BSP selects the amp_core1_bsp that was just created in the previous step.

Shenzhen Guan Chen Electronics Co., Ltd. is a High-tech enterprise that

integrates R&D, design, manufacture of computer peripheral products.The

products include Thunderbolt Docking Station,USB Docking Station,USB Hubs,USB

Adapter, Thunderbolt Cable , SSD Enclosure , HDD Enclosure . Our company adheres to

the principle and motto of Being sincere, Responsible, Practical to meet the

needs of markets and customers with high quality technology and management. We

commit ourselves to new product development and also stress the exploring of

international markets.

Our company owns a professional production team and establishes strict

quality control standard, so we can provide high quality products and service

for customers. We have Grapgic designer,3D Deisnger and Electronic designer to

provides professional OEM/ODM service. Our factory covers an area of 1,000-2000

spare meters, which houses 100-200 workers, so our production capacity reaches

50,000 pieces every day.With more than 10 engineers focusing on research and

development, our private model attracts much among different markets. Over 100

new designed models are released per year.There are also 3 lean production

lines to fullfill small quatity orders production for variety of models.

Our Thunderbolt 3 Docking Station has passed thunderbolt certified by

intel and apple.Our product also all can meet with CE, RoHS, UL, FCC and other

related certification.And our factory also meets legal environmental standards

ensuring your order is delivered. We have a very good reputation at home and

abroad. Our products are mainly exported to Europe, USA and Southeast Asia. We

provide one-stop-service and promote customers achieve rapidly development.

Customer comes First, Quality Ranks First, and Reasonable Price.Guanchen will

be your faithful partner from China.

Ngff Ssd Enclosure,M.2 Ngff Ssd Enclosure,Type-C Ngff M.2 External Ssd Enclosure,Ngff External Ssd Enclosure Shenzhen GuanChen Electronics Co., Ltd. , https://www.gcneotech.com

AMP first phase boot loader

Core 0 app

Core 1 app

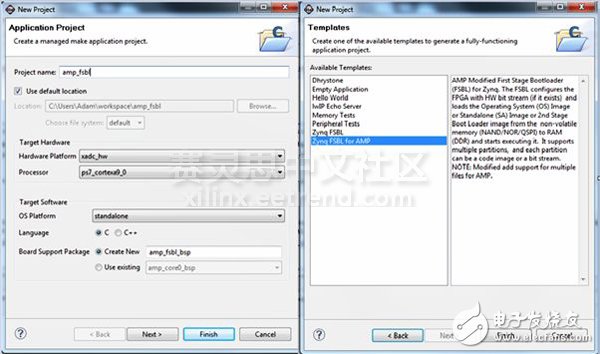

The first step is to create FSBL, select file -> new applicaTIon -> project, so that we can create a FSBL project, implement AMP processing mode, these steps are no different from before, but we choose Zynq FSBL for AMP template instead of the previous Selected Zynq FSBL template.