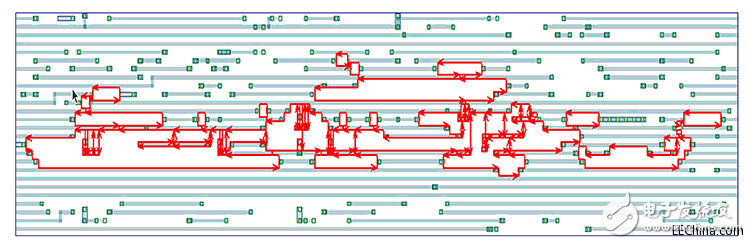

As advanced processes evolve, the circuit design team's ability to load more features and performance on the most advanced on-chip systems is growing. At the same time, they also face many new design challenges. Multiple pattern splitting introduces many significant layout constraints to the design implementation process, and the introduction of FinFET transistors to reduce power consumption and improve performance makes it more complicated because it imposes more restrictions on the placement and routing process. Physical implementation tools for advanced process design must be enhanced for placement, routing, DFM, extraction, and timing after introducing multiple pattern splits and FinFETs. The complexity and number of design rules, including multiple pattern splitting rules, have increased significantly, posing a significant challenge to the routing process. FinFETs also introduce more restrictions, such as voltage threshold sensing intervals, implant layer rules, and so on. These factors will affect the placement, layout planning, and optimization engines, as well as directly affect the utilization and area of ​​the design. Multiple pattern split convergence and timing closure are interdependent, which can increase design convergence time. Figure 1: Long global odd loop violations The routing program must be able to automatically understand the color, detect and fix multiple pattern split violations, and be able to verify it. Traditional DRC violations are often partial, and multiple pattern split violations are different. As shown in Figure 1, they may be global in nature, affecting not only multiple shapes, but also the odd loop repair process. The calculations become extremely dense and difficult. Any interference with the layout can create new multiple pattern split violations, making signal integrity convergence and multiple pattern split convergence challenging. Since pre-existing shapes, power supplies, and ground tracks may result in longer run times for verifying with dense memory, special consideration is given to the routing of metal 1 layers. Conventional techniques like non-preferred slow shifting cannot be used to solve the problem of routing, as these techniques are prohibited in multiple pattern splitting. Multiple pattern splitting uses soft rules to prevent problems, which does reduce the possibility of multiple patterns splitting odd loops, but relying solely on prevention can make the design very passive. Efficient multi-pattern split convergence requires an update to the wiring program architecture, which has its own native tone, verification, and conflict resolution engine. Implementation tools need to consider the interaction between dual pattern splitting limits and FinFET layout limits at each stage of the process, including placement, routing, and optimization. Tools must adhere to a large number of position and path layout rules, such as fin grid alignment rules for standard cells and macros when positioning, minimum area spacing rules, and source-drain docking rules. During placement, the global routing program must consider these rules while computing resources on the dual-pattern structure layer. Typically, this means that the number of networks deployed on these layers will be less, unlike in basic load/capacity calculations. The ability to accurately model the stitch density is very important because the individual units need to be separated for easy wire-to-pin connection. During the placement, the implementation tool must also model the congestion, and estimating the congestion in advance must correlate well with the detailed routing results. In general, advanced process design is optimized to achieve optimal performance and power consumption without affecting the size of the area. Due to the rigorous multi-pattern splitting and FinFET rules and limitations, design utilization and area are increasingly becoming more of a challenge for the design team. Although the FinFET greatly reduces the total power consumption, the dynamic power components are higher (compared to leakage) due to increased parasitic resistance and capacitance as well as pin capacitance. There is a conflict between multiple pattern splitting and timing closure solutions, and signal integrity convergence becomes more difficult. Sometimes the designer can end the "ping-pong effect" between the two, but this means that there are new violations in each of the existing violations. To avoid this problem, tools need to use new technologies, because old technologies such as routing extensions and non-priority slow shifts are no longer effective. The optimization engine must automatically understand the multi-pattern split and FinFET rules to address both power, performance, and area requirements. Due to the introduction of multiple pattern splits, FinFET devices, complex DRC/DFM requirements, more design dimensions and multiple design goals, advanced process design faces a number of major design challenges. Indoor Digital Signage has two styles: vertical and wall-mounted. The floor standing digital signage is used in lobbies, front desks, and store entrances. The wall-mounted digital signage can be displayed horizontally or vertically, and is used in cinemas, restaurants, publicity walls and other places. Video content player,picture media player,digital signage floor standing,digital signage wall mount,Digital signage vertical Jumei Video(Shenzhen)Co.,Ltd , https://www.jmsxdisplay.com