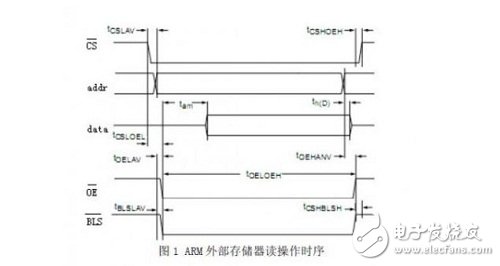

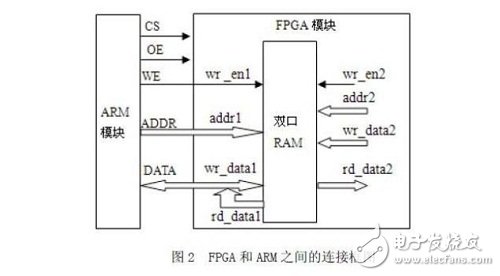

In the design of digital system, FPGA+ARM system architecture has been more and more widely used, FPGA mainly realizes high-speed data processing; ARM mainly realizes system flow control. Human-computer interaction. External communication and functions such as FPGA control. Serial bus interfaces such as I2C and SPI can only achieve low-speed communication between FPGA and ARM; when the amount of data transmitted is large. When high-speed transmission is required, a parallel bus is required to perform high-speed data transmission between the two. The following is based on the ARM processor LPC2478 and the FPGA device EP2C20Q240, taking the read sequence of the ARM external bus as an example to study the parallel bus with high speed transmission between the two; the data bus is 32 bits; and the 1024x32bits SRAM is constructed inside the FPGA. High-speed memory buffer for the ARM processor to quickly read and write FPGA internal data. 1 ARM parallel bus works The external parallel bus of the ARM processor LPC2478 consists of 24 address buses. 32 data buses and a number of control signal lines such as read and write, chip select. According to the system requirements, the data bus width can also be configured into 8-bit, 16-bit and 32-bit working modes. In this design, the signals used in the ARM external bus are: CS.WE.OE.DATA[310].ADDR[230].BLS, etc. CS is the chip select signal, WE is the write enable signal, OE is the read enable signal, DATA is the data bus, ADDR address bus, BLS is the byte group select signal. ARM's external bus read operation timing diagram, as shown in Figure 1. According to the timing of the ARM external parallel bus operation, the read and write operations of the ARM external bus are performed when CS is active low. Since the read operation and the write operation cannot be performed simultaneously, the WE and OE signals cannot simultaneously appear at a low level. The data bus DATA is a bidirectional bus that requires the FPGA to implement bidirectional data transfer. In the timing diagram, the constraint relationship between timings is given. When designing the FPGA, the setup time and retention time of the ARM signal should be met. Otherwise, the read and write instability may occur. 2 FPGA parallel bus design 2.1 FPGA port design A block diagram of the external parallel bus connection between the FPGA and ARM, as shown in Figure 2. Since the internal SRAM memory cell of the FPGA is 32 bits, no byte group selection is required, so the BLS signal can be disconnected. In order to facilitate the fast transfer of data between ARM and FPGA, the internal SRAM of the FPGA must be read and written with the ARM processor, and the data exchange with other logic modules inside the FPGA. Therefore, the SRAM is implemented by dual-port RAM. From the direction characteristics of the port, the DATA port is INOUT (bidirectional) mode, and the remaining ports are IN (input) mode. From the function of the port, clk20m is a global clock. In the implementation, FPGA global clock network should be used, which can effectively reduce the clock delay and ensure the correctness of FPGA timing. ADDR is a 16-bit address bus that is input to the FPGA by an ARM device. DATA is a 32-bit bidirectional data bus, and the design of the bidirectional bus is the focus of the overall design. OE is the read enable signal input to the FPGA by the ARM. WE is the write enable signal input to the FPGA by the ARM. CS is the chip select signal input from the ARM to the FPGA. When the FPGA is not selected by the ARM, it must output a high-impedance state to avoid bus collision. Steel pole is a long cylindrical structure made of steel that is commonly used for a variety of purposes, such as supporting structures, supporting wires or as a decorative element in landscaping. Steel rods are known for their durability, strength, and corrosion resistance, making them a popular choice for outdoor applications. They come in a variety of sizes and shapes depending on the specific requirements of the project. Steel Pole,Galvanized Pole,Electric Power Pole,Stainless Steel Pole JIANGSU HONGGUANG STEEL POLE CO., LTD. , https://www1.hgsteelpole.com