I recently made an FPGA board myself, and accidentally connected the two pins of the PROM to the wrong one, which made it impossible to correctly identify the model of the PROM during configuration, and finally eliminated the problem for one week. Afterwards, I lamented that I was not careful, which led to such low-level mistakes. However, the troubleshooting process forced me to study the xinlin configuration and Jtag-related documents. I combined my own mistakes and I was very impressed. Experience it. Density VCCINT VCCO Range VCCJ Range Packages JTAG ISP Serial Config. Parallel Config. At present, spartan6 and Vertex6 series FPGAs can support multiple configuration modes: the source of the configuration clock can be divided into: Master Modes, Slave Modes, and the data reading modes can be divided into: Parallel, Serial Modes. The following configuration methods are as follows: Master Serial, Slave Serial, Slave Parallel, Master Parallel and other Spartan 6 also support a SelectMAP mode, which can also be divided into Master SelectMAP and Slave SelectMAP. Try these two new configuration methods, so there is no right to speak, so the specific characteristics of these two methods can be found in the relevant datasheet: ug380 and so on. In addition, JTAG can be used for online configuration, but the power-down program cannot be retained.

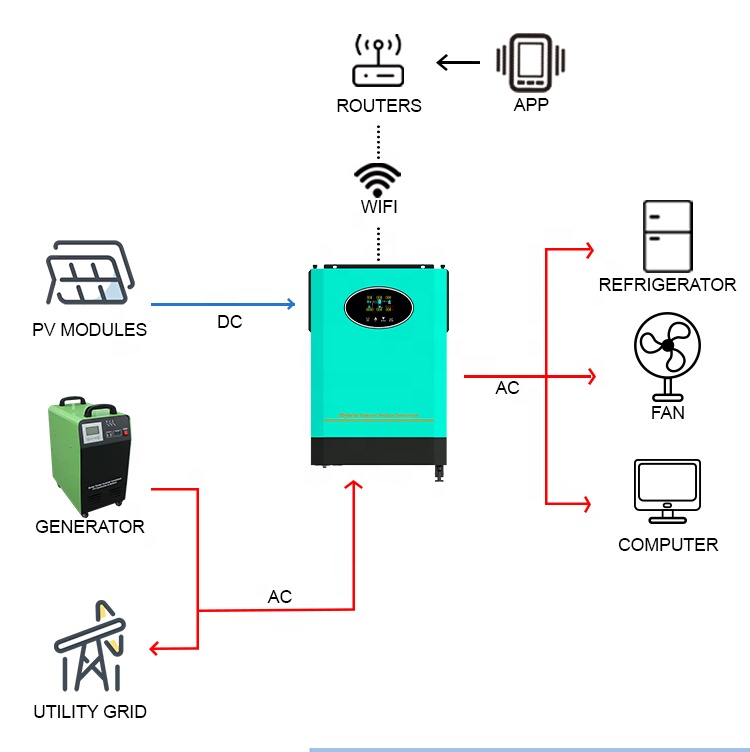

Whaylan On/Off Grid Solar Inverter

Pure sine wave output

On/Off Grid Solar Inverter,Hybrid Inverter With Mppt Charge,pure sine wave solar inverter suzhou whaylan new energy technology co., ltd , https://www.whaylan.com

XCF01S 1 Mbit 3.3V 1.8V - 3.3V 2.5V - 3.3V VO20/VOG20 √ √ &TImes;XCF02S 2 Mbit 3.3V 1.8V - 3.3V 2.5V - 3.3V VO20/VOG20 √ √ &TImes;XCF04S 4 Mbit 3.3V 1.8 V - 3.3V 2.5V - 3.3V VO20/VOG20 √ √ &TImes;XCF08P 8 Mbit 1.8V 1.5V - 3.3V 2.5V - 3.3V VO48/VOG48 FS48/FSG48 √ √ √

XCF16P 16 Mbit 1.8V 1.5V - 3.3V 2.5V - 3.3V VO48/VOG48 FS48/FSG48 √ √ √

XCF32P 32 Mbit 1.8V 1.5V - 3.3V 2.5V - 3.3V VO48/VOG48 FS48/FSG48 √ √ √

XCFxxS is an early rom that does not support faster parallel configurations. It is now fully replaceable with the XCFxxP series, and the XCFxxP also comes with an internal oscillator.

The choice of the specific model in the series depends on your FPGA model. The key is the size of the generated bit file, which cannot be larger than the capacity of the PROM. The specific FPGA recommended with the PROM can be found in the relevant chip data, or PROM data. It is worth mentioning that some large files may be larger than 32M. At this time, two or more PROMs must be cascaded to be sufficient.

The main string mode is described in detail below. The figure is the connection diagram of the main string mode:

[[wysiwyg_imageupload:158:]]

The main string mode is to connect the FPGA, PROM and other devices in the same link according to the JTAG standard. The meaning of the serial connection is that the TDI of the JTAG is connected to the TDI of the first device, and the TDO of the first device is connected. The TDI of a device until the TDO of the last device is connected back to the TDO of the JTAG interface. This forms a chained loop called the JTAG link. The other two wires, TMS (Test Mode Select.) and TCK (Test CLOCK), are connected to each device. Here, the four lines of TCK, TMS, TDI, and TDO have internal pull-ups, so no external pull-up resistor is required. The power supply VREF on the interface is connected to VCCAUX on the datasheet, that is, 2.5V, but I can actually work with 3.3V. I have read the experience of other people on the Internet and the actual measurement is that the power supply is the buffer in the download line. The chip HC244 is powered, so as long as it can meet its level requirements, 2.5 to 5V can theoretically work. After properly connecting these pins, jtag can be used to identify the chip on the link. The board I designed is working in master-slave mode, and the FPGA chip is recognized by JTAG but the PROM cannot be recognized, and the IDCODEs read are all "1". After eliminating the chip problem, the possibility of the problem is concentrated on the four lines. As a result, it is found that the TDI and TCK of the PROM are reversed, resulting in no clock input, so that the explanation is made, and the correction is all normal.

In addition, there are two more important pins on the FPGA: M0, M1. The combination of high and low levels of these two pins represents different modes. The Spartan6 is taken as an example:

ConfiguraTIon Mode M[1:0] Bus Width CCLK DirectionMaster Serial/SPI 01 1, 2, 4 OutputMaster SelectMAP/BPI 00 8, 16 OutputJTAG xx 1 Input (TCK)Slave SelectMAP 10 8, 16 InputSlave Serial 11 1 Input

So here M1 is grounded, M0 is connected to the high level, and it is read in the main string mode.

When the M0 and M1 pins are configured correctly, the FPGA can read data from the PROM at power-on. At this time, the related pins are: CCLK, INTB, DONE, ProgramB, and DIN as shown in the figure. They are connected to clk, OE/RESET, CE, CF, and D0, respectively. The definition of these pins can be found in the PROM and related FPGA documentation. The functions are configuration clock, reset and enable, configuration completion, and serial data transfer. These pins are required to be pulled up on the datasheet except that D0 does not need to be pulled up. However, when many CCLK signals are not pulled down on the development board, I have tried to transfer the unconnected pulldown. I don't know what the impact is. .

The operation sequence of each power-on is as follows:

[[wysiwyg_imageupload:159:]]

The BUSY signal can be disconnected, and the data is transmitted after the CE pulls low and the OE pulls high. After the data transfer in the PROM is completed, DONE is pulled high.

The main configuration flow is divided into four phases: memory clearing, initialization, loading configuration data, and booting the device.

The electrical waveform output of PH1800 is pure sine wave, which has the same quality as practical power supply or household power supply. This waveform is suitable for most electrical equipment, appliances and tools. This pure sine wave unit provides more functions than an improved sine wave inverter because it has a cleaner form of power. Pure sine wave can also reduce the noise generated when applying electrical appliances to a limited extent.