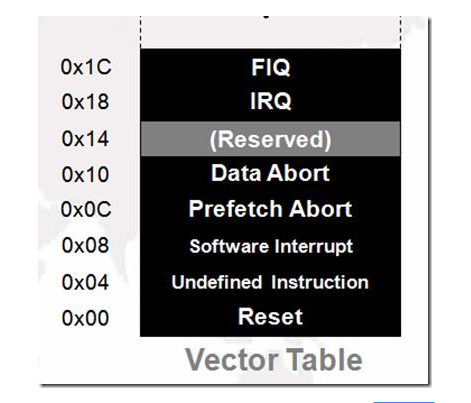

In the past, I have been wondering what is happening with "ARM exceptions, interrupts, and their vector tables" and how they are implemented. I did not expect to see it by chance (ARM System Developer's Guide: Designing and OpTImizing System Software's ARM exception , Interrupts and their vector table chapters are suddenly bright.-ARM embedded system development: the original English version of software design and optimization-I personally feel that this is one of the best translations of ARM books in China, Bido XX The ARM architecture and programming are thousands of times better. Although this book says about software design and optimization, it also talks about a lot of hardware, such as MMU and cache, etc. The talk is wonderful: I just wanted to write a blog about MMU and cache. It is huge, it seems that this period of time to re-read this book before writing. ———————— Let's take a look 2.4 ExcepTIons, Interrupts, and the Vector Table When an excepTIon or interrupt occurs, the processor sets the pc to a speci ï¬ c memory ——When an exception or interrupt occurs, the processor sets the PC to a special memory address. This address is called the interrupt vector table. The interrupt vector table entry is the branch entry for interrupts and exceptions ((* ^ __ ^ *) Hee hee ..., this translation is bad, but everyone knows it). The memory map address 0x00000000 is reserved for the vector table, a set of 32-bit -The memory mapped address 0x00000000 is reserved for the interrupt vector table. In some processors, the interrupt vector table address is 0xffff0000. Some operating systems such as Linux can take advantage of this feature (in fact, wince uses 0xffff0000 as the address of the interrupt vector table, but it is strange that the address of the interrupt vector table of the ADS bootloader of Uron is 0x00000000, which is estimated to be determined by the compiler) . When an exception or interrupt occurs, the processor suspends normal execution and ——When an exception or interrupt occurs, the processor suspends the normally executed program and starts to load the interrupt vector table. Each interrupt entry contains a branch instruction pointing to a speci ï¬ c routine (this does not know how to translate). â– Reset vector is the location of the ï¬ rst instruction executed by the processor when power ——The reset vector is the first instruction executed by the processor when the power is turned on. This instruction branches to the initialization code. â– Unde ï¬ ned instruction vector is used when the processor cannot decode an instruction. ——Undefined instruction vector, used when the processor cannot decode the instruction â– Software interrupt vector is called when you execute a SWI instruction. The SWI ——Software interrupt vector ........ The software interrupt instruction is commonly used in the operating system. ——The pre-fetch termination vector occurs when the processor attempts to fetch an instruction address, and the access is not properly granted, the actual termination occurs at the decoding stage â– Data abort vector is similar to a prefetch abort but is raised when an instruction attempts ——The data termination vector is similar to the prefetch termination, but it occurs when the instruction attempts to access the data, and the memory does not have the correct access permission. ——The interrupt request vector is used in a program that is normally executed by an external hardware interrupt. It can only be used when IRQs are not masked by cpsr. ================================================== ================================== Summary: This interrupt vector search is implemented by hardware. The hardware specifies that the PC jumps to 0xffff0000 / 0x00000000 (see the compiler for details). In the past, I always learned from the perspective of software, which is a big mistake. Monochrome Lcd-Cog,Graphics Lcd Display,Transmissive Cog Lcd Module,Positive Cog Lcd Module Huangshan Kaichi Technology Co.,Ltd , https://www.kaichitech.com

download link:

)

address. The address is within a special address range called the vector table. The entries

in the vector table are instrucTIons that branch to speci ï¬ c routines designed to handle a

particular exception or interrupt.

words. On some processors the vector table can be optionally located at a higher address

in memory (starting at the offset 0xffff0000). Operating systems such as Linux and

Microsoft's embedded products can take advantage of this feature.

starts loading instructions fromthe exception vector table (see Table 2.6). Each vector table

entry contains a form of branch instruction pointing to the start of a speci ï¬ c routine:

is applied. This instruction branches to the initialization code.

instruction is frequently used as themechanismto invoke an operating systemroutine.

â– Prefetch abort vector occurs when the processor attempts to fetch an instruction froman

address without the correct access permissions. The actual abort occurs in the decode

stage.

to access data memory without the correct access permissions.

â– Interrupt request vector is used by external hardware to interrupt the normal execution

fl ow of the processor. It can only be raised if IRQs are not masked in the cpsr.